爱心捐赠

ESP32

qt

注解处理器

药物化学

jsp

安卓分区

汇编

keil

collections

STM32CubeMX

AppCube

two sum

电路

junit5

idea

系统架构

资损

web课程与设计

mutex

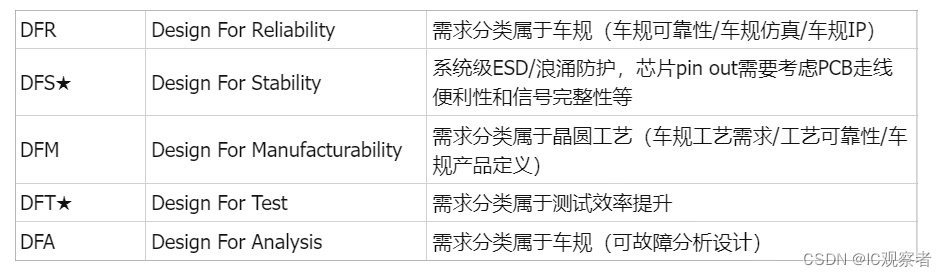

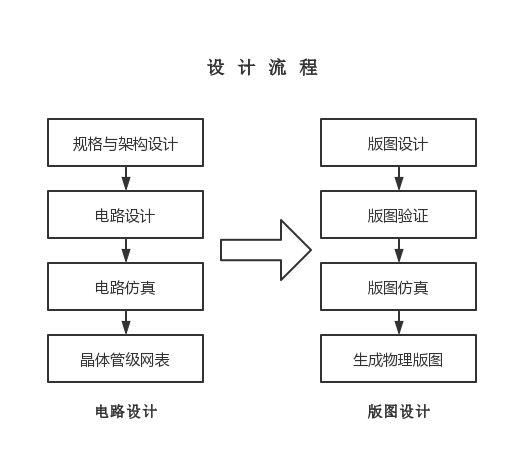

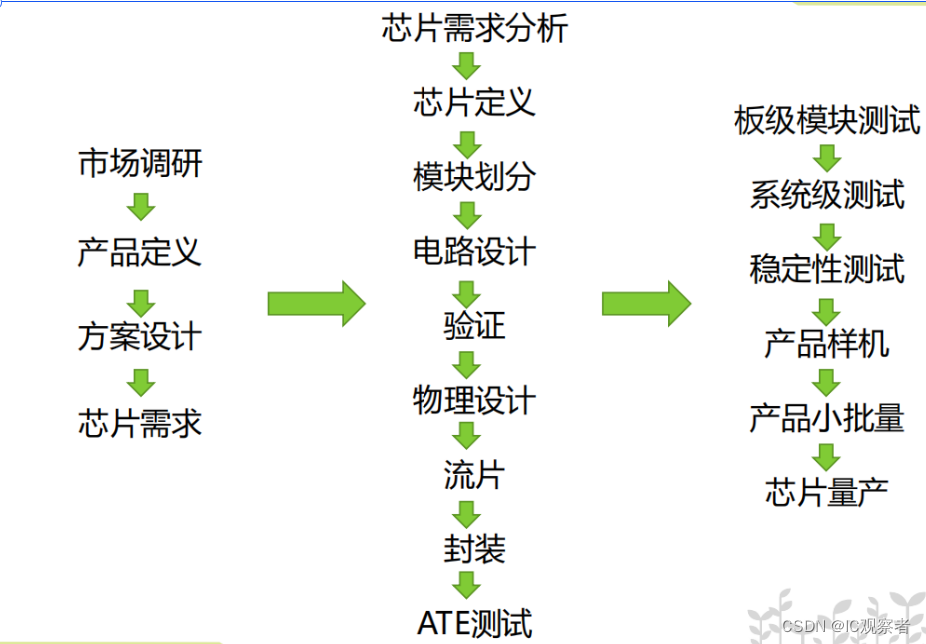

芯片设计

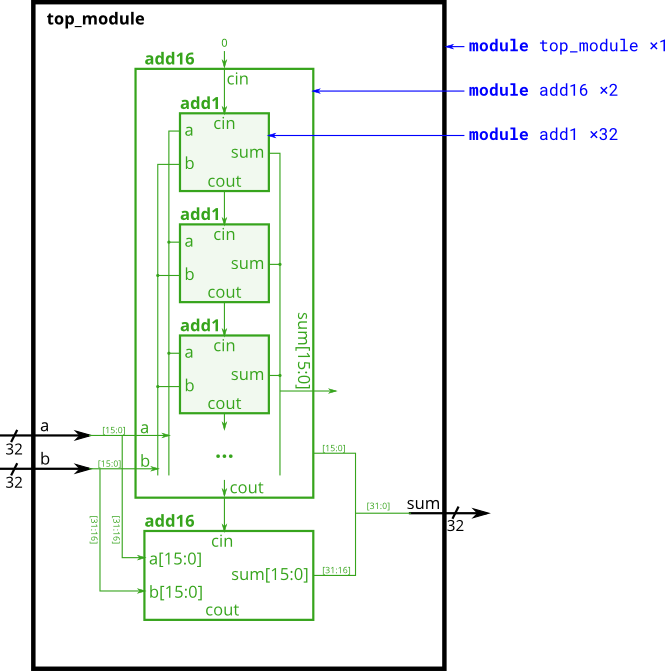

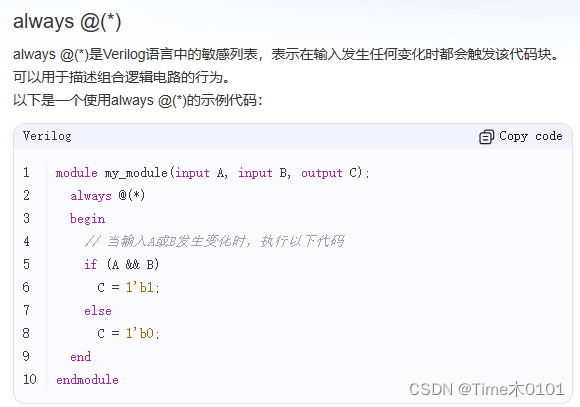

2024/4/12 15:51:38HDLBits-Verilog学习记录 | Verilog Language-Modules(2)

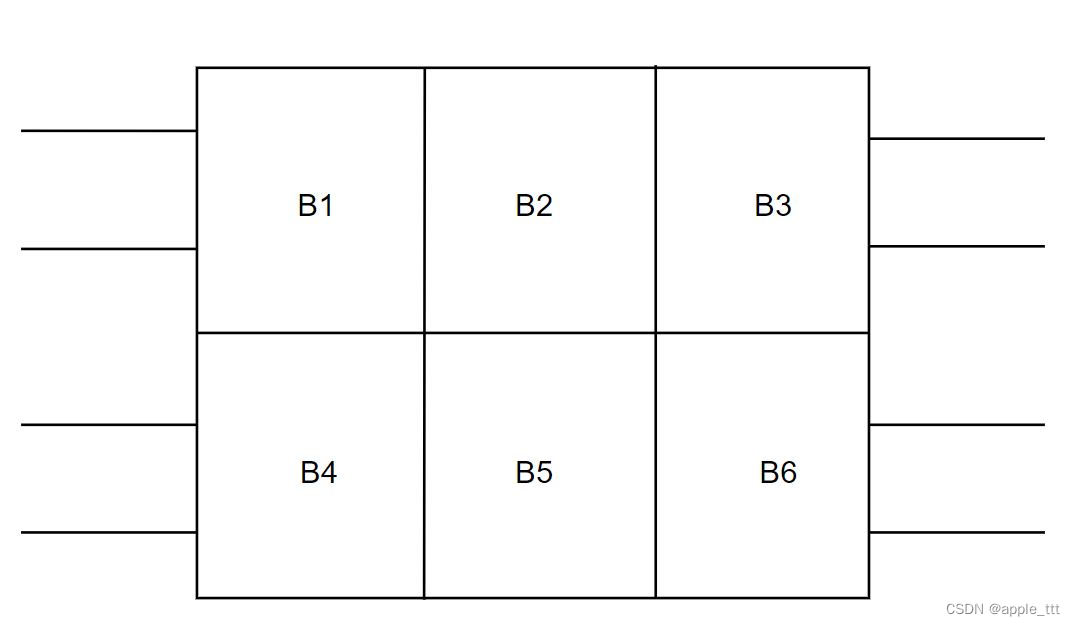

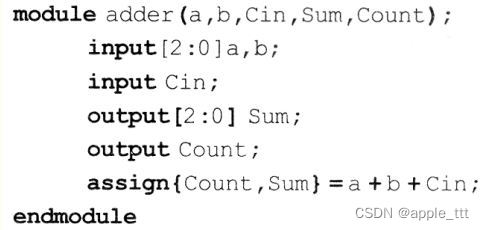

文章目录 25.Adder 1 | Module add26.Adder 2 | Module fadd27.Carry-select adder28.Adder-subtractor 25.Adder 1 | Module add

practice: You are given a module add16 that performs a 16-bit addition. Instantiate two of them to create a 32-bit adder. O…

芯片验证学习-设计知识补充学习4-锁存器和触发器、寄存器区别?如何实现时钟门控

锁存器和触发器、寄存器区别?如何实现时钟门控 1、锁存器、触发器、寄存器区别?2、clocking gate时钟门控背景?3、实现门控时钟方法?1)与门2)锁存门控3)锁存门控毛刺的解决方法:拓展:为什么不用寄存器解决毛刺问题呢,要用锁存器?1、锁存器、触发器、寄存器区别?

锁…

芯片工程师求职题目之CPU篇(3)

1. 什么是cache(缓存)?它的工作原理是什么?

Cache是少量的快速内存。它位于主存储器和中央处理器之间。每当CPU请求memory位置的内容时,首先检查cache中是否有此数据。如果数据存在于cache中,CPU直接从cache中获得数据。这是更快…

芯片科普 | IC新人入行如何选择岗位?

IC行业的产业环节众多且环环相扣,每个环节都需要不同职责的工程师。这篇文章主要以IC设计环节的岗位为主,帮大家提供择岗的思路。

建议先了解行业

从个人求职的角度出发,建议先了解一些概况,是为了确定自己是否适合这个行业&…

从事IC工作,IC公司招人都看重哪些方面?

比起去年拿着40W招不到应届生的局面,今年IC企业在招聘方面似乎更偏向“理性”了一些。 但在当前的市场环境下,依然还是人才供不应求。 当求职者们还在内心OS“求职难”的时候,招聘者也在深受“招聘难”的困扰。 也就是说,岗位机会…

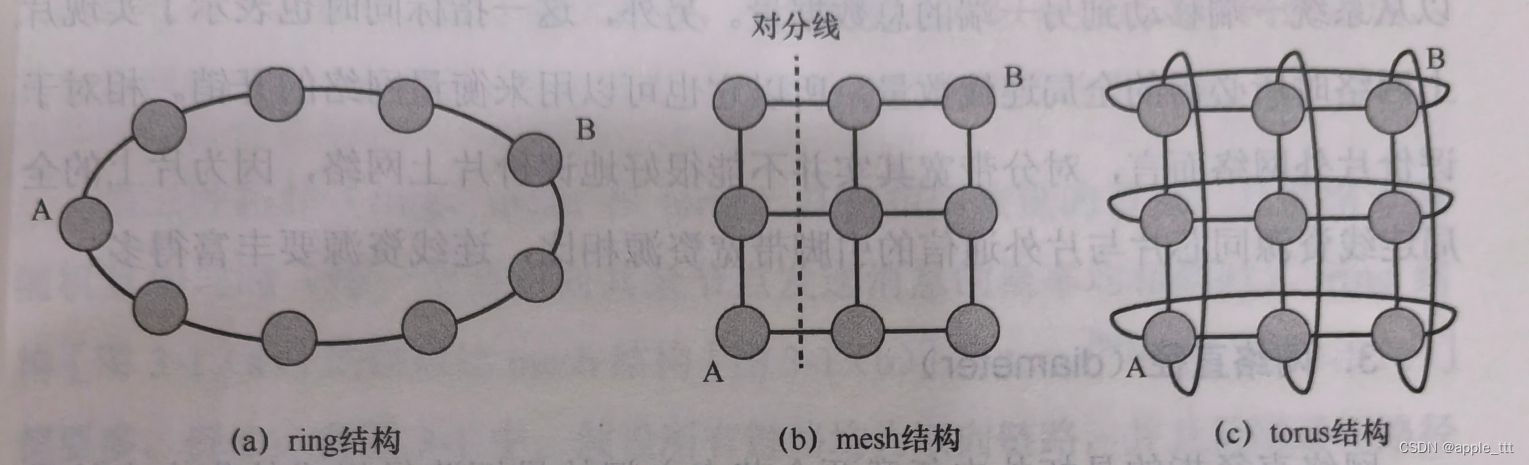

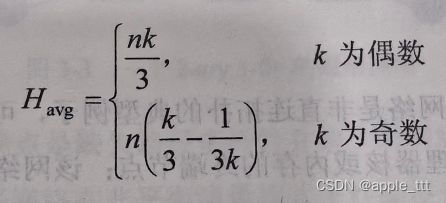

片上网络NoC(3)——拓扑指标

目录

一、概述

二、指标

2.1 与网络流量无关的指标

2.1.1 度(degree)

2.1.2 对分带宽(bisection bandwidth)

2.1.3 网络直径(diameter)

2.2 与网络流量相关的指标

2.2.1 跳数(hop coun…

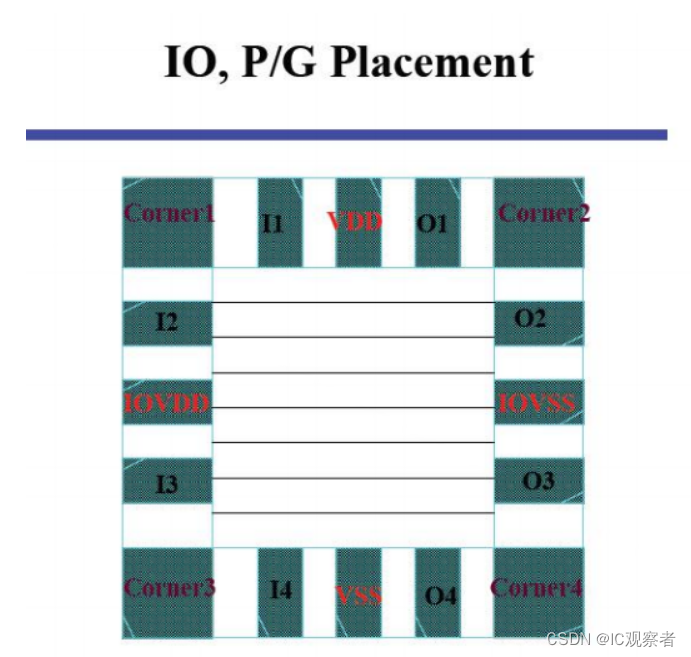

数字IC丨后端设计是个啥?

最近的私信咨询里,很多同学分不清数字IC设计前端和后端的区别,前端设计似乎很容易理解,简单来说就是敲代码的,只不过没有用C和python,用的是硬件描述语言Verilog。

但一说到后端设计,很多同学就懵了&#…

小白转行IC设计可行吗?

“我是上海211材料小硕毕业,目前在台积电做设备工程师,刚入职一个月,觉得这个岗位不太适合自己,想自学一些数字电路设计或者ic design相关的工作,学校里没学过这些专业课,请问企业会要我这种半路出家的吗&a…

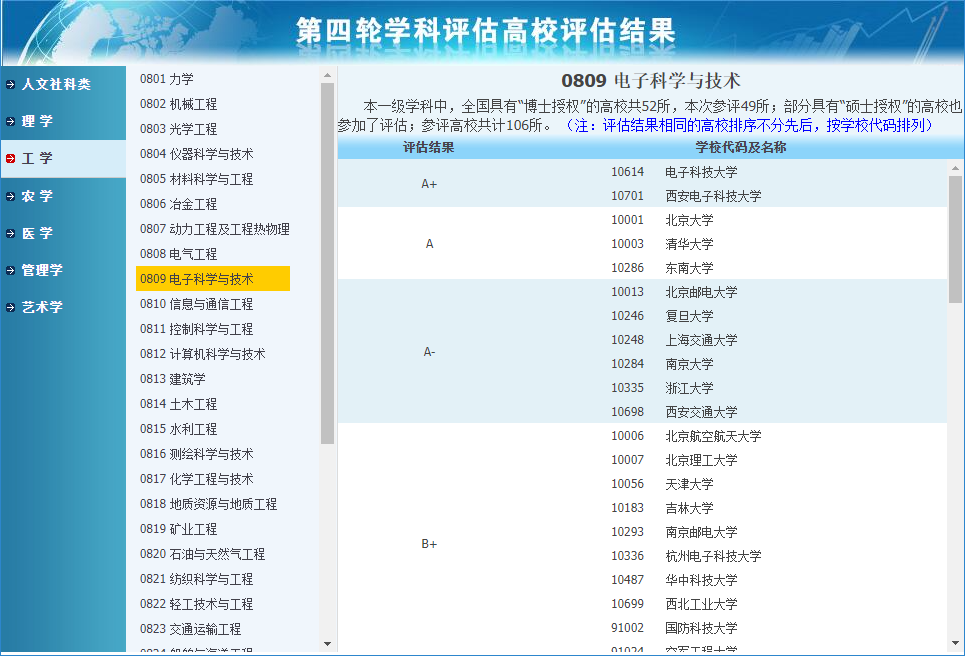

微电子专业深度盘点:哪所大学芯片最强?强在哪?(第3弹)

目前国内微电子高校的天花板就是示范性28所微电子学院,我们之前已经讲过了19所,这期视频就来盘点后面这9所高校。 这是微电子高校盘点的第三期,前两期指路:

微电子专业 | 哪所大学芯片最强?强在哪?&#x…

如何看待OPP给应届生开出40W+的offer?

昨天突然看到一个IC行业的话题上了热榜前三,今天再看更是一度冲到第一。 “如何看待 OPPO 给应届生开出 40w 的待遇?”

再一看还是去年提的问题,突然就被冲上了问答榜单,我怀疑是绿厂自己动的手,但我没有证据。 不过还…

《深入浅出SSD:固态存储核心技术、原理与实战》----学习记录(三)

第3章 SSD存储介质:闪存

3.1 闪存物理结构

3.1.1 闪存器件原理

1978年诞生的世界上第一块固态硬盘就是基于DRAM的。但由于保存在DRAM中的数据有掉电易失性,当然还有成本因素,所以现在的固态硬盘一般都不采用DRAM,而是使用闪存…

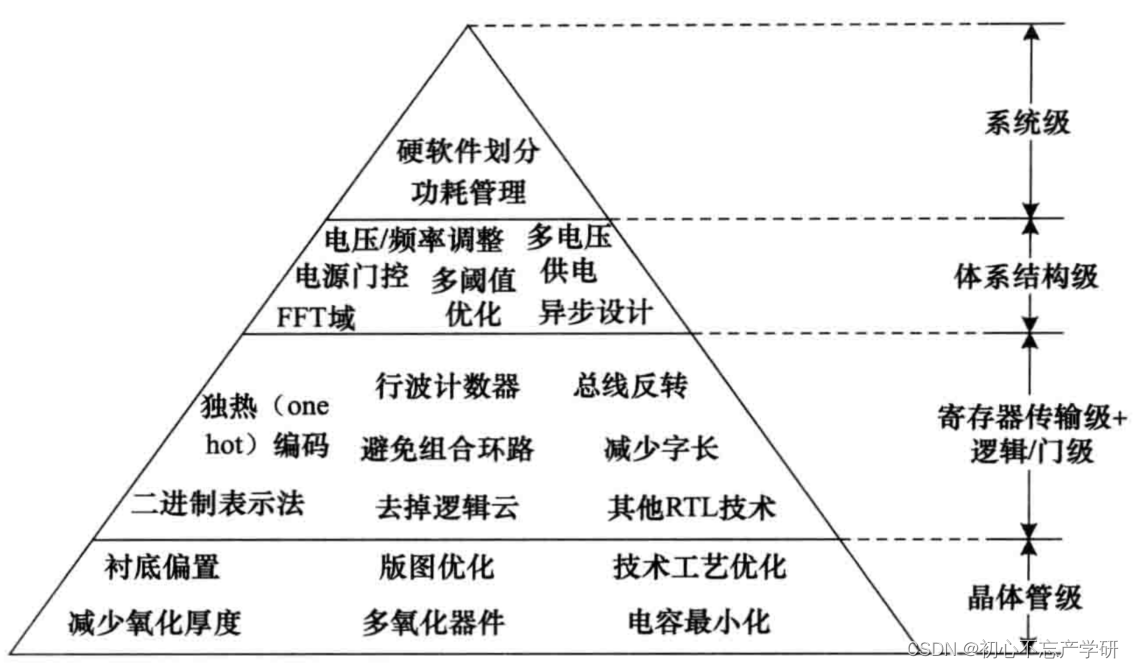

《低功耗方法学》翻译——第一章:介绍

第一章:介绍

1.1 概述

在过去的二十年时间里,复杂芯片的设计已经经历了一系列巨大的改变。20世纪80年代,引入了基于语言的设计和综合。在20世纪90年代,设计重用和IP成为主流设计。在过去的几年里,低功耗设计再次开始…

单片机开发——电子天平秤的芯片设计

人们把用电磁力平衡被称物体重力的天平称为电子天平秤。其特点是称量准确可靠、显示快速清晰并且具有自动检测系统、简便的自动校准装置以及超载保护等装置。

电子天平秤的四个重要性能指标:就是天平的稳定性、天平的灵敏性、天平的正确性和天平示值的不变性。所谓…

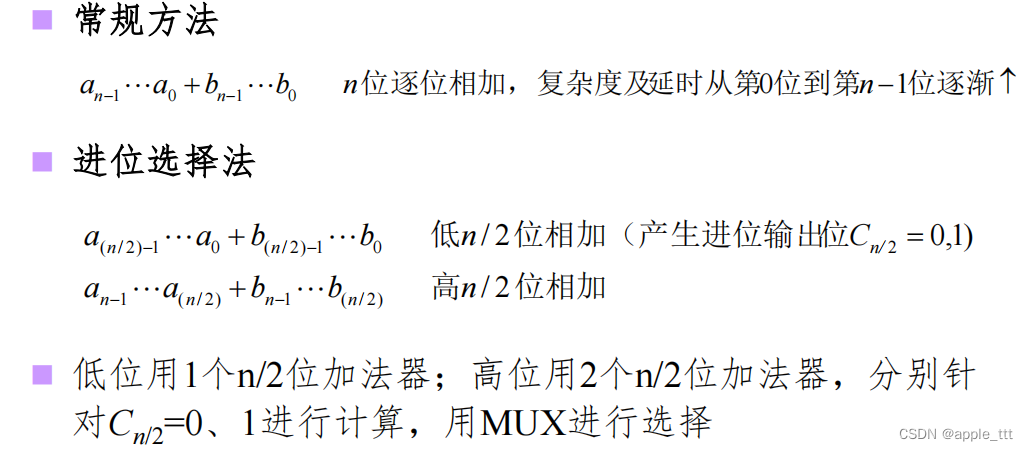

运算电路(1)——加法器

一、引言 微处理器是由一片或少数几片大规模集成电路组成的中央处理器。这些电路执行控制部件和算术逻辑部件的功能。微处理器能完成取指令、执行指令,以及与外界存储器和逻辑部件交换信息等操作,是微型计算机的运算控制部分。它可与存储器和外围电路芯片…

FPGA时序分析与约束(6)——综合的基础知识

在使用时序约束的设计过程中,综合(synthesis)是第一步。

一、综合的解释 在电子设计中,综合是指完成特定功能的门级网表的实现。除了特定功能,综合的过程可能还要满足某种其他要求,如功率、操作频率等。 有…

RTL编码(1)——概述

一、RTL级描述 RTL(Register Transfer Level)级:寄存器+组合逻辑,其功能与时序用Verilog HDL(以下简称Verilog)或VHDL代码描述。 RTL描述包含了同步数字电路最重要的三个特征:组合逻…

模拟IC设计工程师成长日记

很多IC设计的新人,不知道进入IC设计行业后会有哪些成长和学习的地方。 很多初入IC设计职场的人也都会比较恐慌,成长进步需要一个时间和经验的积累 今天给大家找了一个叫“模拟IC设计“攻城狮”的成长日记供大家参考. 以模拟IC设计工程师的身份进入职场&a…

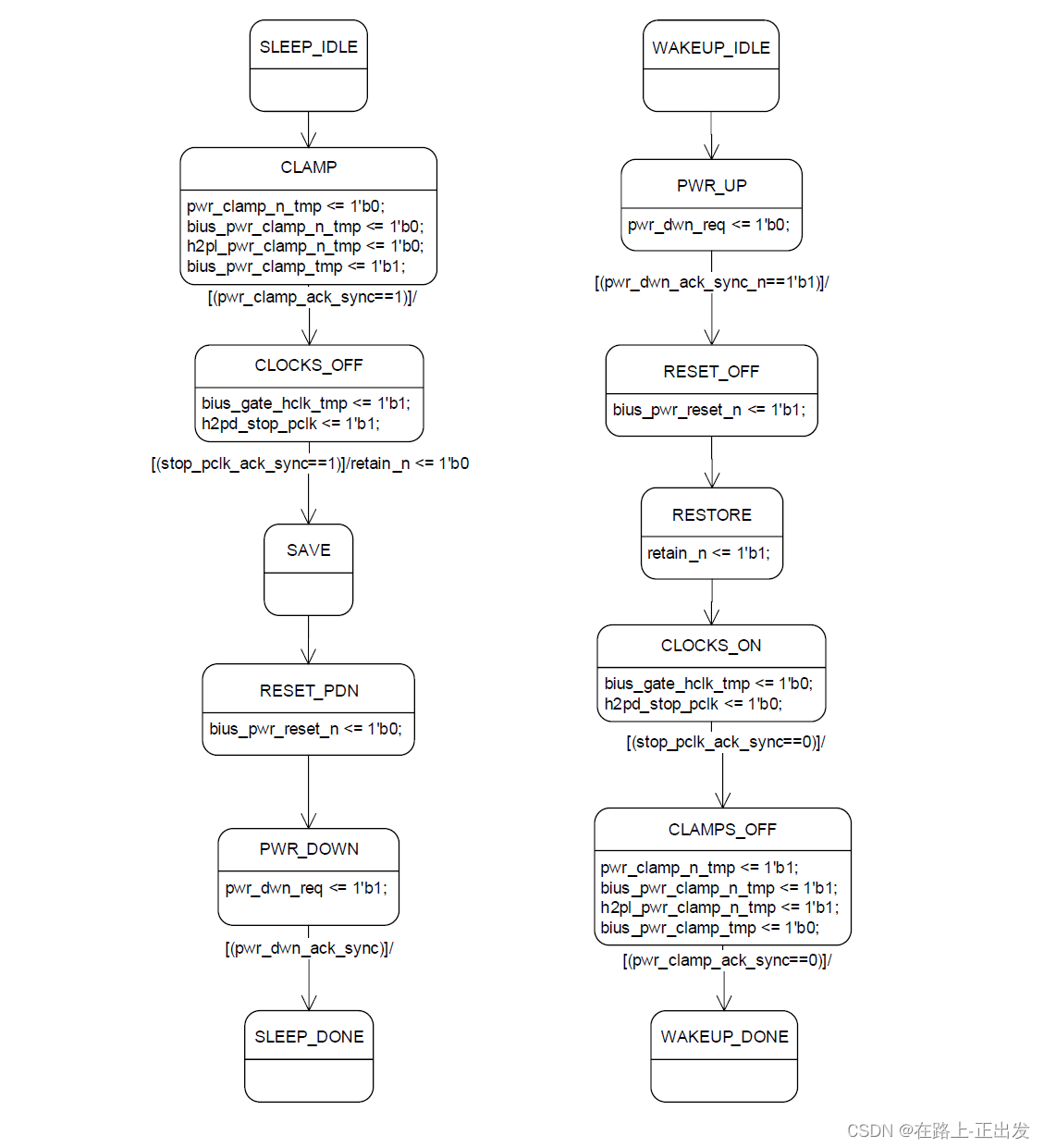

《低功耗方法学》翻译——第八章:低功耗IP设计

第八章:低功耗IP设计

前几章从系统架构师和芯片设计者的角度讨论了低功耗设计。本章从复杂IP设计工程师的角度来描述低功耗设计,如处理器、DSP、USB、PCI Express和总线基础架构。到目前为止,我们已经假设IP是相对固定的,我们必须…

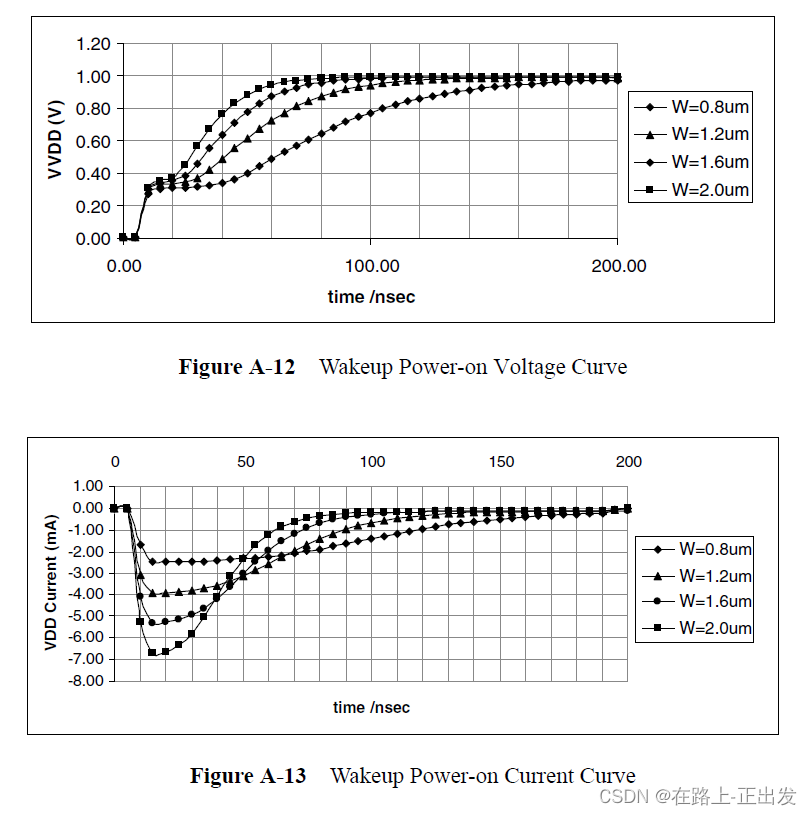

《低功耗方法学》翻译——附录A:睡眠晶体管设计

附录A:睡眠晶体管设计

休眠晶体管是PMOS或NMOS高VT晶体管,用于在待机模式下关闭设计部件的电源。PMOS休眠晶体管用于切换VDD电源,因此被称为“header开关”。NMOS休眠晶体管控制VSS电源,因此被称为“footer开关”。在90 nm及以下…

FIFO设计核心问题

1.什么是FIFO?

FIFO (First-In-First-Out) 是一种先进先出的数据交互方式,在数字ASIC设计中常常被使用。FIFO按工作时钟域的不同又可以分为:同步FIFO和异步FIFO。

使用异步FIFO可以在两个不同的时钟域之间快速而方便的传输数据,…

片上网络NoC(4)——直连拓扑

目录

一、前言

二、直连拓扑

三、总结 一、前言 本文中,我们将继续介绍片上网络中拓扑相关的内容,主要介绍直连拓扑,在此之前,我们已经介绍过了拓扑的指标,这将是继续阅读本文的基础,还没有了解相关内容…

练习十一:简单卷积器的设计

简单卷积器的设计 1,任务目的:2,明确设计任务2.1,目前这部分代码两个文件没找到,见第5、6节,待解决中。 ,卷积器的设计,RTL:con1.v4,前仿真和后仿真,测试信号…

为什么很多人从FPGA转IC前端岗?哪个前景好?

很多入行不久的朋友潜意识里会认为FPGA是很高深的东西,能掌握FPGA的一定都是极其厉害的人。

其实,这是一个误解。

我们所讨论的FPGA只是基于已有的FPGA芯片去做后端排列组合的工作内容,而不是设计制造新的FPGA芯片,世界上能做这…

一个亿,在一家芯片公司可以烧多久?

一、前言

这个问题我分别问了几个芯片公司的创始人。 有说2年的(某中等规模电路,成熟制程的MCU芯片公司); 有说1年的(某AI算力芯片公司); 有说半年的(通讯SoC芯片,需要搭…

牛客网Verilog刷题 | 入门特别版本

文章目录 1、 VL1 输出12、VL2 wire连线3、 VL3 多wire连接4、VL4 反相器5、VL5 与门6、VL6 NOR 门7、VL7 XOR 门8、VL8 逻辑运算10、VL10 逻辑运算211、VL11 多位信号12、VL12 信号顺序调整13、VL13 位运算与逻辑运算14、VL14 对信号按位操作15、VL15 信号级联合并16、VL16 信…

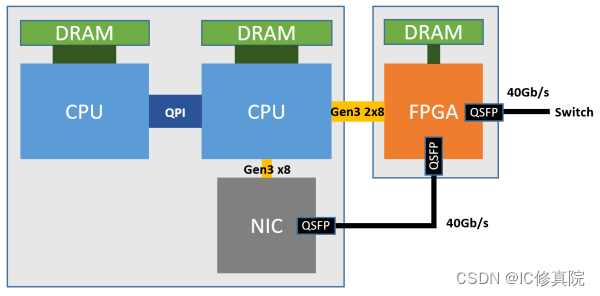

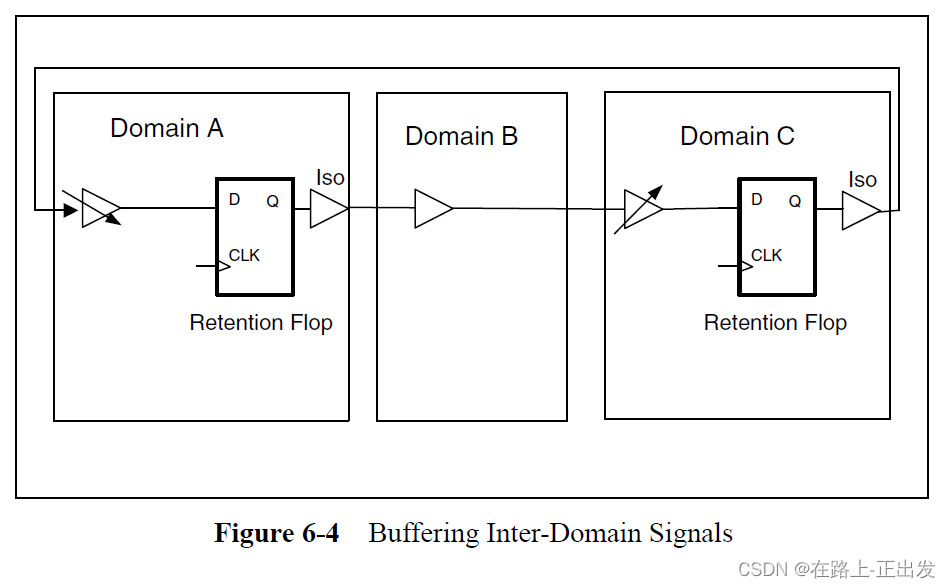

《低功耗方法学》翻译——第六章:功率门控的架构问题

第六章:功率门控的架构问题

本章讨论了植入功率门控设计中涉及的一些架构问题。特别地,它解决了分区、层次结构和多个功率门控域的问题。

6.1 层次化结构和功率门控

芯片架构的可扩展方法是有价值的,因为今天在芯片上的系统设计经常在随后…

入行IC | 一文读懂FPGA与ASIC的区别

IC行业的范围很广,有数字、模拟不同的研究方向,也有设计、制造、封测不同的产业环节、还有FPGA、ASIC等不一样的芯片领域。

遇到过很多想要入行、转行IC的同学,都有“选FPGA还是ASIC”的问题。区分概念往往是做选择的前提,所以首…

工程师思维是什么?芯片工程师要有哪些思维习惯?

芯片工程师有知识基础和工作技能就够了?

我不同意!

至少这个说法漏掉了很重要的思维,柏拉图说过,“思维是灵魂的自我谈话”。

在IC行业,思维对工程师来说是非常重要的。所以芯片工程师应该具备怎样的核心思维习惯呢…

微电子专业 | 哪所大学芯片最强?强在哪?(深度盘点)

今天来聊聊微电子高校,提到微电子专业,肯定不得不说9所首批示范性微电子学院,今天就来盘他们!

类似于专业设置、培养方案、课程设置这类信息,在学校官网上都是可以直接搜索到的,就不和大家赘述了。

这里主…

芯片验证学习随记1-随机约束,线程与UVM组件

分享常见写法,以便工作查询使用

TreeExplorer

声明随机变量的类 权重分布 集合成员和inside 条件约束 打开或关闭约束

选择不同约束组合 内嵌约束

soft : 软约束: 当内外部约束不满足时, 软约束优先级更低 随机数函数

randomize() -> pre_ 和post 简单的随机化 约束数组…

HDLBits-Verilog学习记录 | Getting Started

Getting Started

problem: Build a circuit with no inputs and one output. That output should always drive 1 (or logic high).

答案不唯一,仅共参考:

module top_module( output one );// Insert your code hereassign one 1;endmodule相关解释…

芯片工程师求职题目之CPU篇(1)

1. RISC和CISC架构有什么不同?

RISC全称是Reduced Instruction Set Computer。

CISC全称是Complex Instruction Set Computer。

RISC架构有更少的指令,且这些指令比较简单,比如固定指令长度、更少的寻址模式。CISC架构有更多的指令&#x…

[Note]对于补码的思考

补码是什么? 我想先举一个例子,二进制中,假设我们用3个位表示3,对应二进制是011,2对应的二进制是010,23,对应的是011010101,对应的二进制是5。 可以看到,在不溢出的情况下…

Verilog零基础入门(边看边练与测试仿真)-状态机-笔记(7-10讲)

文章目录 第七讲第八讲第九讲第十讲 第七讲

1、最简单的状态机-三角波发生器

1、两种状态的代码:

//最简单的状态机,三角波发生器;

timescale 1ns/10ps

module tri_gen(clk,res,d_out);

input clk;

input res;

o…

IC设计端各岗位薪酬对比(建议收藏)

根据人才招聘平台对于2023年已有数据统计,芯片工程师岗位均薪为26012元,位列全行业第一。

这里需要说明一下,这里的“芯片工程师”涵盖了设计、制造、封测等多环节岗位。并非只有芯片设计岗。 从行业招聘薪酬同比增速来看,电子技…

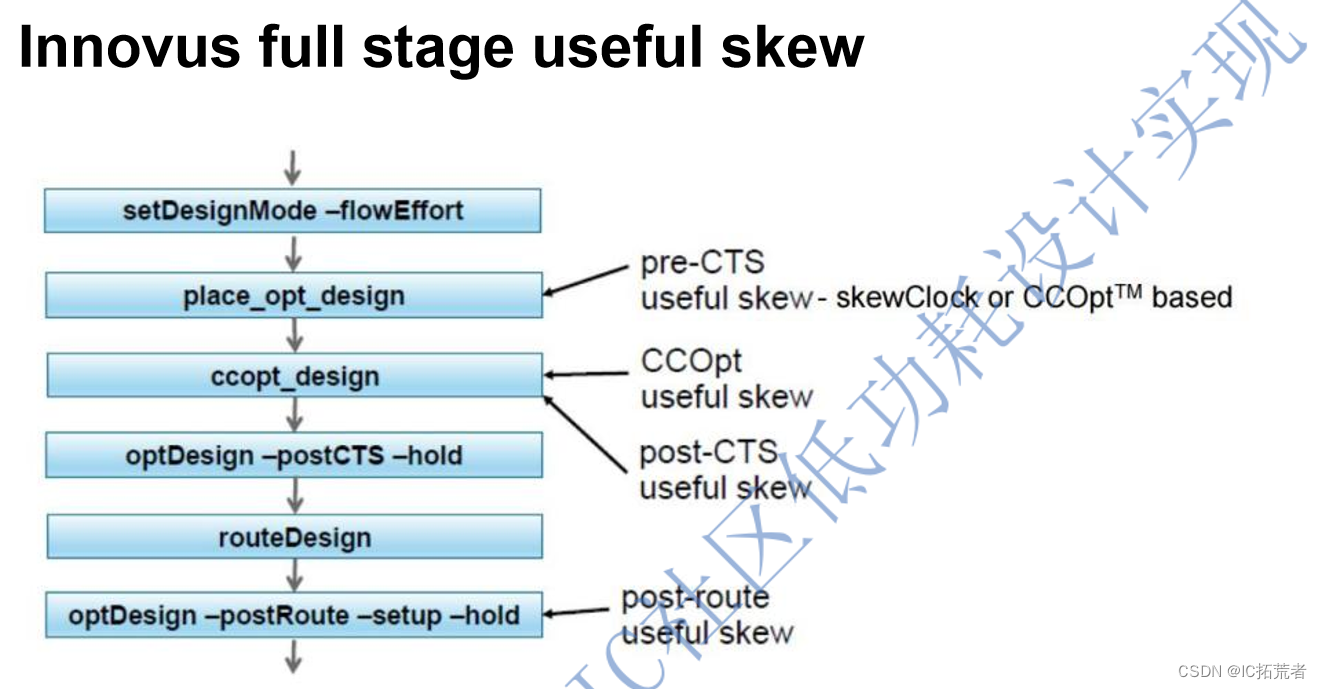

数字后端设计实现之自动化useful skew技术(Concurrent Clock Data)

在数字IC后端设计实现过程中,我们一直强调做时钟树综合要把clock skew做到最小。原因是clock skew的存在对整体设计的timing是不利的。 但是具体到某些timing path,可能它的local clock skew对timing是有帮助的,比如如下图所示。 第一级FF到第…

哪些专业跟芯片有关?

IC产业作为最近两年的一个新风口,薪资高,待遇好。成了很多人想要跳槽的行业。尤其是毕业生处于供不应求的状态。那么哪些专业跟芯片有关?

哪些专业跟芯片有关?

(1)微电子学与固体电子学、微电子科学与工程…

当你想要成为一名IC设计工程师时,不妨先看看这篇文章

目前整个 IC行业发展的非常迅速,但是最近网上也出现了一些唱衰的声音,认为IC行业已经开始内卷了。

那是不是内卷呢?这就要看市场的供求关系。

据我所知,不管是大企业还是小企业,都投入大量的人力物力去招聘ÿ…

IC设计行业都有哪些不错的公司(外企篇)

当越来越多的同学选择IC修真院之后,咨询的问题就从最开始的该怎么入行IC设计,慢慢变成了该怎么选择offer,该怎么挑选公司?

非科班的同学本就对IC行业知之甚少,更别提具体的公司状况,他们不清楚为什么不推荐…

转行IC的人都会问到的五个问题

随着IC设计的“出圈”,无论是行业发展还是薪资涨幅,都算得上盛名在外了。现在很多非微电子科班的理工科专业的同学都想转行芯片行业,大量求职者的涌入使得企业的用人门槛和工作强度逐渐变高。

经过一年的“转行潮”,越来越多的同…

给微电子专业学生的一些建议,如何避免踩坑?

建议往往都是有时效性的,就拿高考报志愿来说,20年前的土木专业的那套说法并不适用于今天,也说不准10年后最好的专业可能真的是“生化材环”。

当下来说,微电子专业无疑是志愿选择中较为优秀的方向,但如果仅仅把时间往…

微电子专业深度盘点:哪所大学芯片最强?强在哪?(第2弹)

众所周知,国内高校微电子专业都以示范性28所微电子学院为代表,其中又分前9所和后19所,之间的区别就在于:

前9所是支持建设示范性微电子学院,后19所是支持筹备建设示范性微电子学院。建设与筹备建设之间的区别很容易理…

科普 | IC工程师到底有哪些?(设计+制造)

随着摩尔定律和技术的发展,芯片集成度也越来越高,与之伴随的就是岗位愈加细分。芯片产业链很长且环环相扣,每一个环节都需要不同的工程师角色分工协作。

很多人以为芯片工程师就是单纯搞芯片的工程师,殊不知这其中可能要分十几个…

学员追访丨器件转行IC的一点心得分享

图片

大家好,我是验证十期学员L,一个中科院微电子所的器件硕士,理论上来说,算是原本想学微电子,结果还是进了材料的坑。目前通过转行IC,现在已经拿到某企业芯片验证工程师的offer,年薪33W。

这…

什么是模拟IC设计?

什么是模拟IC设计?

模拟IC就是处理连续性光、声音、速度、温度等自然模拟信号的IC,主要是用来对模拟信号进行采集、放大、形式变换和功率控制的。 如果按照功能给模拟器件分类,可以分成电源链(管理电池与电能)和信号链…

学员追访丨双非硕士大厂逆袭

数字验证二期-李同学:陕科大软件工程硕士

offer:北京奕*伟(西安分部)-17K14

毕业后的现实

我是属于典型的双非院校的硕士,本科读的专业是电气工程及其自动化专业,硕士阶段主要跟导师做FPGA。

从去年的…

数字IC设计工程师成长四阶段

朋友,你有入行三年、五年、十年的职业规划吗?你知道你所做的岗位未来该如何成长吗?

IC行业的发展近几年是突飞猛进的,有越来越多的人才想要或已经踏进了IC行业的大门。很多同学在入行IC之前,都会抱着满腹对职业发展的…

一篇文章带你认识芯片分类及代表企业

芯片的分类方式可以有很多种,如果我们随机采访10位业内大佬,也许会得到10种不同的答案。 举个例子,按照处理信号方式可分为模拟芯片和数字芯片。 按照设计理念可分为可分为通用芯片和专用芯片。 按照应用领域可分为航天级芯片,汽车…

低成本IC上岸攻略—IC设计网课白嫖篇

数字电路基础

清华大学 王红主讲:数字电子技术基础 西安电子科技大学 任爱锋主讲:数字电路与逻辑设计

模拟电路基础

上交大 郑益慧主讲:模拟电子技术基础 清华大学 华成英主讲:模拟电子技术基础

半导体物理:

西…

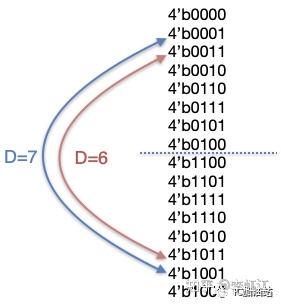

芯片工程师求职题目之设计基础篇(1)

1. 进制转换

会算数值在二进制、八进制、十进制以及十六进制之间的任意转换。

会算数值的正码、反码、补码、BCD码。 2. 什么是格雷码(Gray code),它有什么优点。

在一组二进制编码中,若任意两个相邻的数值还有1位二进制数不同,则称这种编…

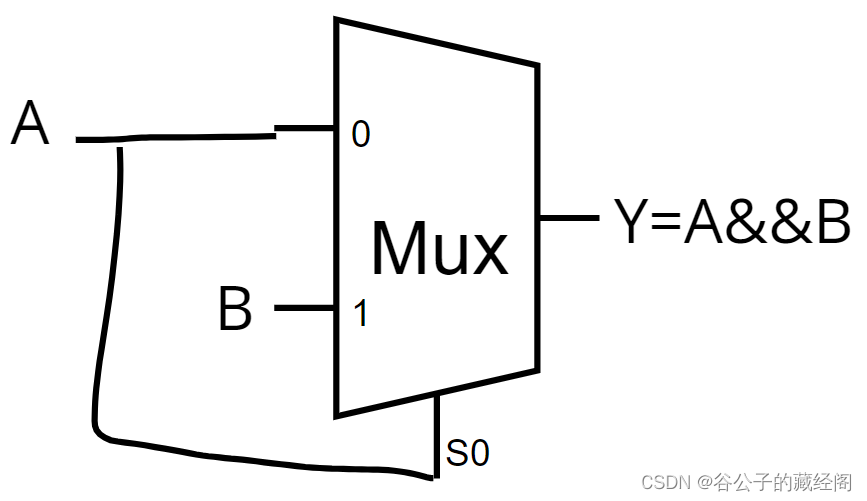

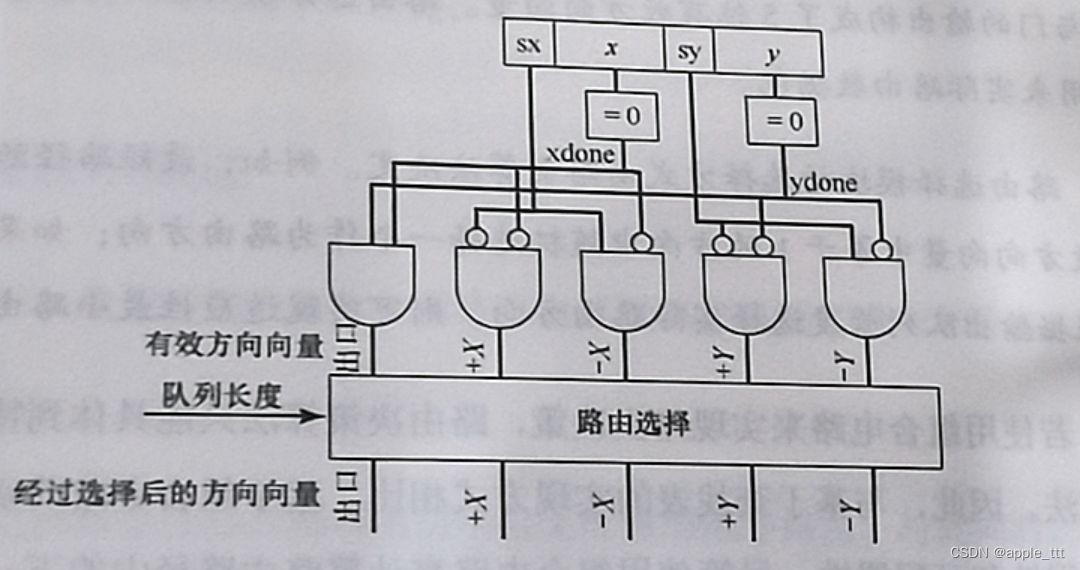

片上网络NoC(6)——路由算法

目录

一、概述

二、路由算法的类型

三、避免死锁

四、实现

4.1 源路由实现

4.2 基于节点查找表的路由实现

4.3 组合电路实现

五、总结 一、概述 路由算法(routing algorithm),即决定数据包在网络拓扑中从起点到终点路径的算法。路由算…

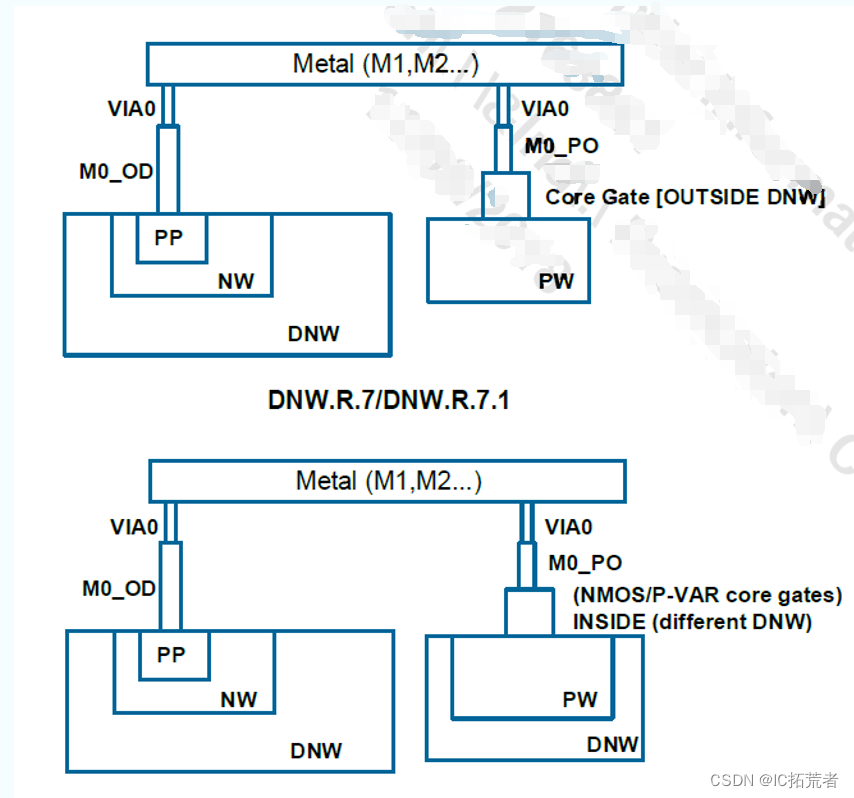

EDA云实证Vol.13:暴力堆机器之王——Calibre

Siemens的Calibre是业内权威的版图验证软件,被各大Foundry厂广泛认可。用户可以直接在Virtuoso界面集成Calibre接口,调用版图验证结果数据,使用起来极为方便。

今天,我们就来聊聊这款软件。

版图验证是芯片设计中非常重要的一环…

边缘计算与物联网的核心 —— 低功耗芯片

一、低功耗芯片

在边缘计算与物联网(IoT)中,低功耗芯片扮演了至关重要的角色,主要体现在以下几个方面: 延长设备寿命:物联网设备通常需要部署在难以更换电池或不方便进行频繁维护的环境中,比如…

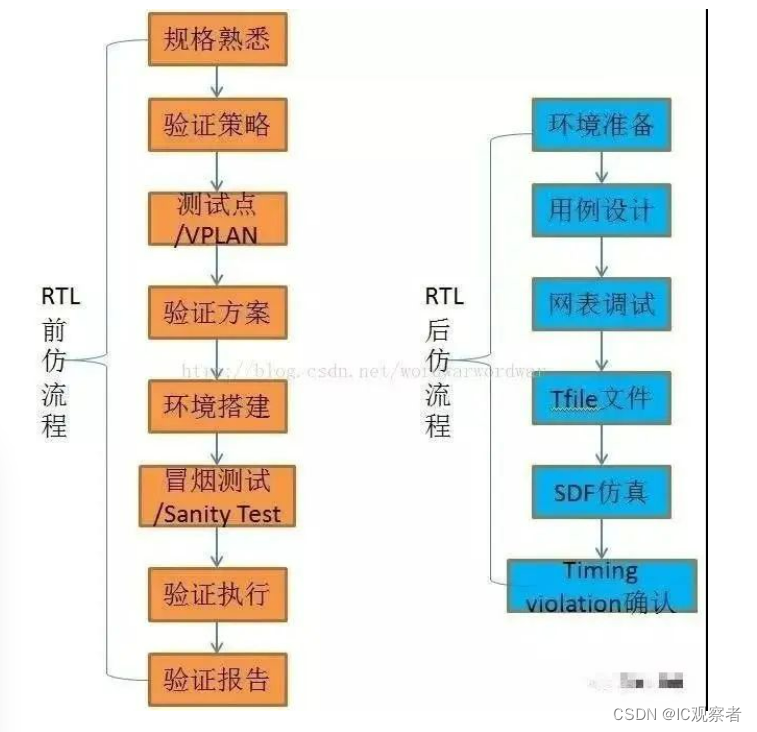

ic验证的主要工作流程和验证工具是什么?

验证其实是一个“证伪”的过程,从流程到工具,验证工程师的终极目的都只有一个:

发现所有BUG,或者证明没有BUG,以保证芯片功能性能的正确性和可靠性。

验证环节对于一颗芯片的重要性也是不言而喻的:

从项…

芯片SoC设计你了解吗?

数字IC设计根据岗位性质一般包含SOC设计,前端设计,ASIC设计,逻辑设计,IP设计,CPU设计等。 有人说:做IP设计就是翻译官,做SOC设计就是连连看。 SoC设计是做什么的?与IP设计有什么不同…

后端设计PNR一点总结

条条大路通罗马

在追求极致PPA的过程中,时序问题总是可以解决

方法总比困难多

关键问题其实就是控制delay

不多不少,简单总结二十一条(欢迎大家评论区继续发挥): module padding的设置,可以有效解决congestion问题,factor自己try,命令:setPlaceMode -place_global…

数字IC后端实现 |TSMC 12nm 与TSMC 28nm Metal Stack的区别

下图为咱们社区IC后端训练营项目用到的Metal Stack。

芯片Tapeout Review CheckList 数字IC后端零基础入门Innovus学习教程 1P代表一层poly,10M代表有10层metal,M5x表示M2-M6为一倍最小线宽宽度的金属层,2y表示M7-M8为二倍最小线宽宽度的金…

《低功耗方法学》翻译——附录B:UPF命令语法

附录B:UPF命令语法

本章介绍了文本中引用的所选UPF命令的语法。

节选自“统一电源格式(UPF)标准,1.0版”,经该Accellera许可复制。版权所有:(c)2006-2007。Accellera不声明或代表摘录材料的准确性或内容&…

数字后端设计实现 | 数字后端PR工具Innovus中如何创建不同高度的row?

吾爱IC社区星球学员问题:Innovus后端实现时两种种不同高度的site能做在一个pr里面吗?

答案是可以的。 Innovus支持在同一个设计中中使用不同的row,但需要给各自子模块创建power domain。这里所说的不同高度的row,有两种情况。

1…

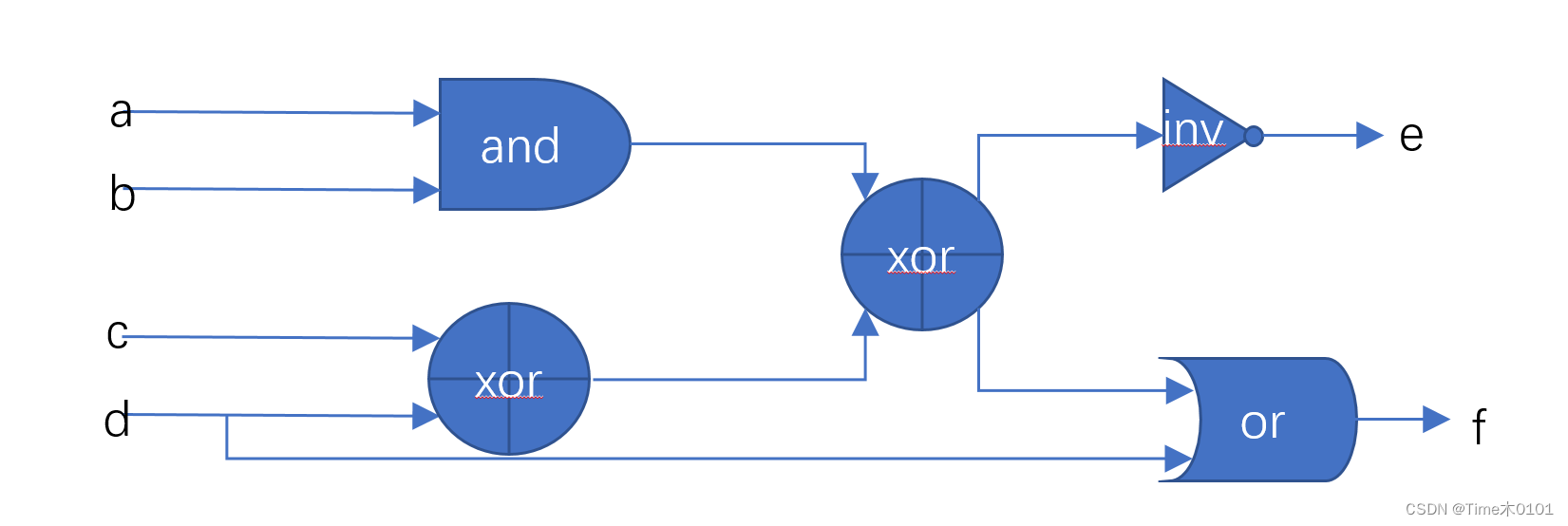

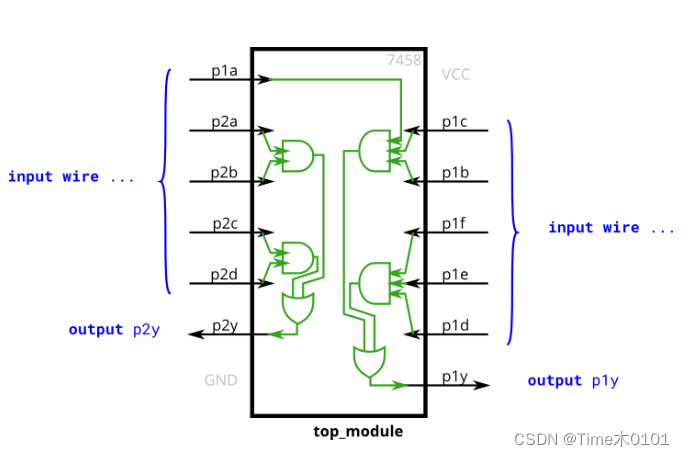

HDLBits-Verilog学习记录 | Verilog Language-Basics(2)

文章目录 9.Declaring wires | wire decl10. 7458 chip 9.Declaring wires | wire decl

problem:Implement the following circuit. Create two intermediate wires (named anything you want) to connect the AND and OR gates together. Note that the wire that feeds the …

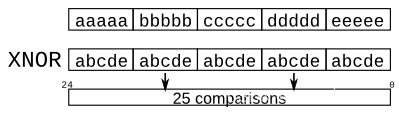

HDLBits-Verilog学习记录 | Verilog Language-Vectors

文章目录 11.vectors | vector012.vectors in more detail | vector113.Vector part select | Vector214.Bitwise operators | Vectorgates15.Four-input gates | Gates416.Vector concatenation operator | Vector317.Vector reversal 1 | Vectorr18. Replication operator | …

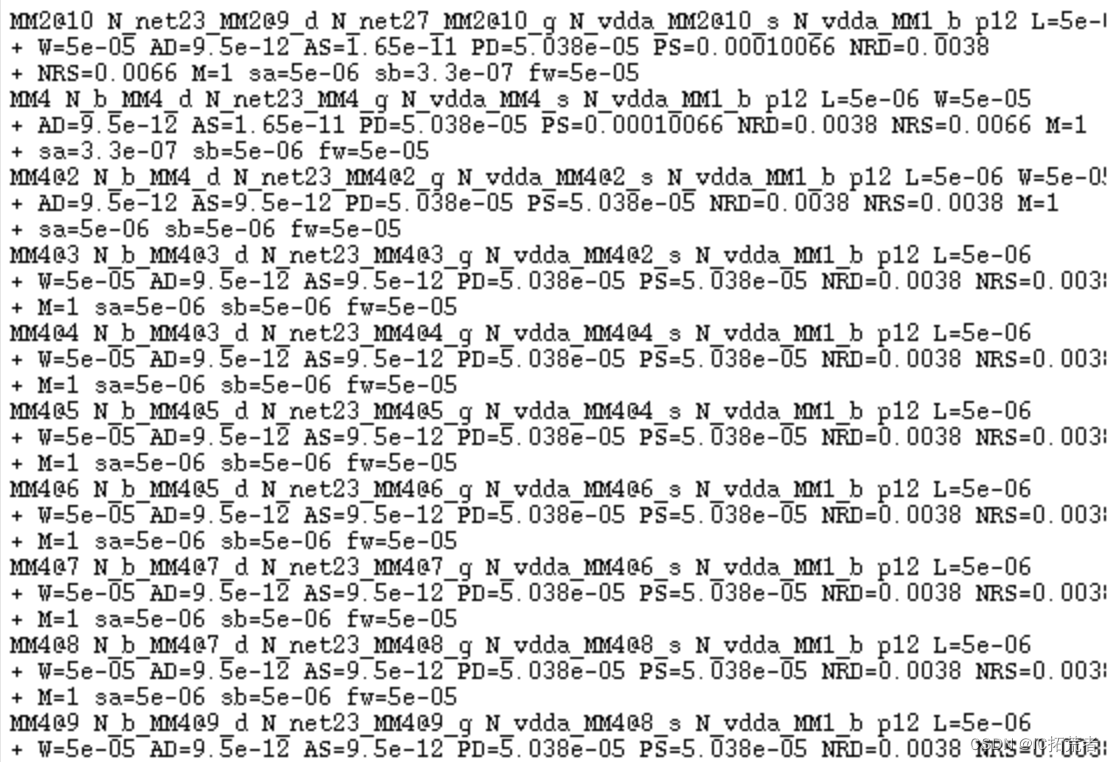

Calibre PEX Hspice Netlist提取步骤(数模芯片提取spice netlist流程)

在数模混合芯片中,通常模拟需要数字模块通过calibre工具来提取Hspice netlist用于功耗仿真。注意这里的spice netlist和做Calibre的spice netlist是不太一样的。

另外在做calibre pex时需要确保当前的design LVS已经pass。否则功耗仿真可能会不准。

Calibre LVS常…

数字IC后端设计实现之Innovus update_names和changeInstName的各种应用场景

今天吾爱IC社区小编给大家分享下数字IC后端设计实现innovus中关于update_names和changeInstName在PR中的具体使用方法。

update_names

1)为了避免和verilog语法保留的一些关键词,比如input,output这些,是不允许存在叫这类名字的…

Verilog零基础入门(边看边练与测试仿真)-时序逻辑-笔记(4-6讲)

文章目录 第四讲第五讲第六讲 第四讲

1、计数器 代码:

//计数器

timescale 1ns/10ps

module counter(clk,res,y);

input clk;

input res;

output[7:0] y;reg[7:0] y;

wire[7:0] sum;//1运算的结果(1࿰…

干货!数字IC后端入门学习笔记

很多同学想要了解IC后端,今天大家分享了数字IC后端的学习入门笔记,供大家学习参考。 很多人对于后端设计的概念比较模糊,需要做什么也都不甚清楚。 有的同学认为就是跑跑 flow、掌握各类工具。

事实上,后端设计的工作远不止于此。…

HDLBits-Verilog学习记录 | Verilog Language-Modules(1)

文章目录 20.Module21.Connecting ports by position | Moudle pos22.Connecting ports by name | Module name23.Three modules | Module shift24.Modules and vectors | Module shift8 20.Module

practice:You may connect signals to the module by port name or port posi…

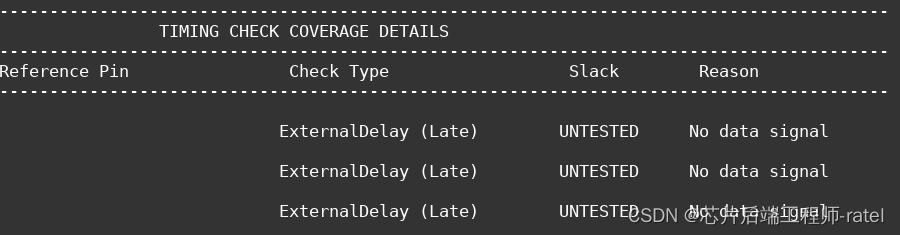

innovus中时序路径debug及命令使用详解?

写在前面:发现place结果所有与outport相关的timing check都找不到?

刚开始怀疑是sdc约束问题,check了input sdc文件及enc.dat/mmmc/mode/func.sdc

看一下是否设置了set_false_path.当然也可以用命令报出来:

report_timing -unconstrained …